1. Jurnal [Kembali]

4. Analisa [Kembali]

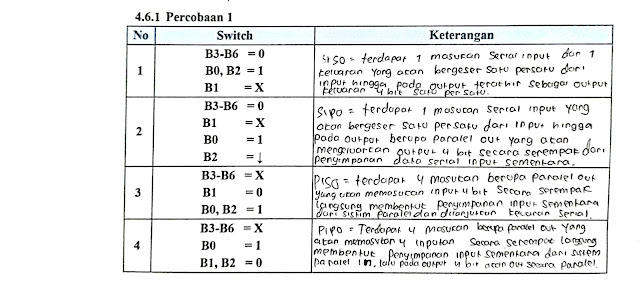

- Kondisi 1 : B3 s.d. B6 = 0 , B0 dan B2 = 1 ,B1 = X

Pada kondisi ini yaitu switch B3 sampai B6 terhubung pada input set aktif low pada JK flip-flop yang diatur input logika 0, lalu input switch B0 dan B2 diatur pada inputan berlogika 1, pada input B1 dapat diabaikan. Berdasarkan kondisi diatas diperoleh bahwa kondisi rangkaian akan memproses output yaitu pada kondisi operasi rangkaian SISO, karena pada jenis IC JK flip-flop yang digunakan input set dan input reset aktif low, sehingga saat input B3 sampai B6 pada masukkan set diberi input logika 0 dan input B0 diberi logika 0, lalu diumpankan ke gerbang NOT, sehingga rangkaian kondisi operasi tetap, maka input B1 dan B2 yang akan ambil alih sebagai pengaturan keluaran output Q. Saat input switch B2 berlogika 1 maka output gerbang AND memiliki karakteristik kinerja seperti sinyal clock kemudian output gerbang AND diumpankan pada input clock pada IC JK flip-flop. Pada switch B1 yang diabaikan dapat diatur input D flip flop berlogika 0, sesuai prinsip kerja rangkaian SISO, saat memasukkan 1 data diinputkan sesuai pengaturan input D, maka clock yang bekerja pada aktif high akan memproses input sesuai kinerja register geser yang akan menggeser tiap satu masukan input yang diatur sesuai aktif kerja clock, yang menggeser input dari kiri (bit pertama) ke kanan (bit ke empat). Lalu dilanjutkan proses serial out yang bergeser hingga pada bit ke-4, maka setiap satu input akan masuk pada rangkaian dan akan mengeser input serial in sebelumnya yang diinputkan, saat clock aktif high yang akan menggeser input hingga bit ke-4 terakhir sebagai pembaca serial out.

- Kondisi 2 : B3 s.d. B6 = 0 , B1 = X , B0 = 1 , B2 = ↓

Pada kondisi ini, input switch B3 sampai B6 berlogika 0, lalu pada switch B1 diatur pada kondisi input D flip flop diabaiikan diatur input berlogika 1 dan 0, pada input switch B0 diatur pada logika 1 terhadap input reset dan B2 berlogika 1 dan 0 berubah-ubah diatur pada input gerbang AND.

Pada kondisi ini diperoleh bahwa kondisi rangkaian akan memproses output yaitu operasi rangakaian SIPO, karena input S dan R masing-masing IC berlogika 0 membuat IC dalam operasi tetap, maka saat switch B2 diatur berlogika 1, maka kondisi rangkaian akan membentuk operasi serial in pada input sesuai pengaturan input B1 yang diabaikan (berlogika 0 atau 1) tergantung input bit yang dimasukkan bergeser hingga pada bit ke-4 hingga diperolen penyimpanan data sementara serial in, lalu dilanjutkan pada pengaturan B2 berlogika 0 setelah input serial yang dinginkan selesai, maka B2 akan menggantikan fungsi clock menjadi 1 kali clock dari operasi gerbang AND yang menandakan hasil keluaran output 4 bit berhenti yang menjadi titik output paralel out 4 bit serempak terbaca pada masing-masing bit.

- Kondisi 3 : B3 s.d. B6 = X , B1 = 0 , B0 dan B2 = 1

Pada kondisi ini, input switch B3 sampai B6 dapat diabaikan yang berarti dapat kita atur pada 2 operasi yaitu logika 1 dan logika 0, lalu pada switch B1 diatur pada kondisi input berlogika 0, pada input switch B0 dan B2 diatur pada logika 1 terhadap input reset dan gerbang AND.

Pada kondisi ini diperoleh bahwa kondisi rangkaian akan memproses output yaitu operasi rangakaian PISO, karena input S dan R masing-masing IC berlogika abaikan membuat IC dalam operasi tetap dan kondisi set, maka saat switch B2 diatur berlogika 1, maka kondisi rangkaian akan membentuk operasi paralel in pada input sesuai pengaturan input B3 s.d. B6 yang diabaikan (logika 1) membentuk input set pada input "1111" 4bit yang dimasukkan akan diperoleh input serempak 4 bit sesuai pengaturan input set yang diinginkan 4 bit, sehingga diperoleh penyimpanan data sementara 4 bit pada paralel in "1111", lalu dilanjutkan proses serial out yang bergeser hingga pada bit ke-4, maka setiap satu input akan masuk pada rangkaian dan akan mengeser input paralel in sebelumnya yang diinputkan, saat clock aktif high yang akan menggeser input "1111" hingga bit ke-4 terakhir sebagai pembaca serial out.

- Kondisi 4 : B3 s.d. B6 = X , B0 = 1 , B1 dan B2 = 0

Pada kondisi ini input switch B3 sampai B6 dapat diabaikan yang berarti dapat kita atur pada dua operasi yaitu logika 1 dan 0, lalu pada switch B0 yaitu reset diatur logika 0, lalu input switch B1 dan B2 diatur input D flip flop dan input gerbang AND berlogika 0.Pada kondisi ini diperoleh bahwa kondisi rangkaian akan memproses output yaitu operasi rangakaian PIPO, karena input S dan R masing-masing IC berlogika abaikan membuat IC dalam operasi tetap dan kondisi set, maka saat switch B2 diatur berlogika 1, maka kondisi rangkaian akan membentuk operasi paralel in pada input sesuai pengaturan input B3 s.d. B6 yang diabaikan (logika 1) membentuk input set pada input "1111" 4bit yang dimasukkan akan diperoleh input serempak 4 bit sesuai pengaturan input set yang diinginkan 4 bit, sehingga diperoleh penyimpanan data sementara 4 bit pada paralel in "1111", lalu dilanjutkan pada pengaturan B2 berlogika 0 setelah input serial yang dinginkan selesai, maka B2 akan mematikan fungsi clock dari operasi gerbang AND yang menandakan hasil keluaran output 4 bit berhenti yang menjadi titik output paralel out 4 bit serempak terbaca pada masing-masing bit.

5. Link Download [Kembali]

0 komentar:

Posting Komentar